# **LOW TEMPERATURE CO-FIRED CERAMICS**

# 【LTCC低温共烧陶瓷多层基板 LTCC Multilayer Substrates

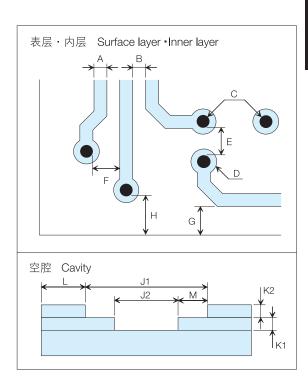

#### ■ 结构图 Construction

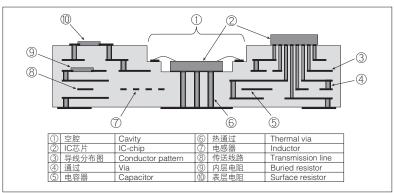

#### ■ 特点 Features

- ●是根据KOA公司独家的收缩控制技术和层叠技术的尺寸精度良好的多层基板。

- ●由于精细的线路、模式,可以高密度布线。

- 可以通过L.C.带状传输线内层实现小型化。

- ●由于低感电损失陶瓷和低损失导体,高频特性优良。

- ●由于接近硅的热膨胀系数,是适于装配裸片的基板。

- 通过在裸片安装部设置热观测器,可提高放热性。

- 因为陶瓷的关系, 耐热、耐湿性良好。

- ●对应欧盟RoHS。

- Excellent size accuracy, by KOA's original shrinkage control technology and multi layer technology.

- The high-density wiring by the fine line and pattern is available.

- Miniaturization is possible by burying L, C and Strip-line.

- By the uses of low dielectric-loss ceramics and low loss conductors, the substrates excel in the high frequency characteristic.

- As the thermal expansion coefficient is close to silicon's, the substrates are suitable for the bare chip mounting

- By preparing the thermal vias under bare chips, the substrates are excellent in the heat dissipation.

- The substrates are outstanding in heat resistance and humidity resistance due to the ceramics used.

- Products meet UE-RoHS requirements.

### ■ 收缩控制技术 Shrinkage Control Technology

LTCC在煅烧时会收缩,但通过精密控制材料、流程,实现了低于±0.05%的位置精度。

KOA公司的收缩控制技术有如下特点。

- ① 由于也能保持高度方向的精度,因而内层从动部件的特性,精度良好。

- ② 形成空腔时,可以形成稳定的空腔结构。

Although LTCC shrinks in the firing process, KOA has realized the position accuracy in  $\pm 0.05\%$  or less by precisely controlling the process and the material. There are the following features in the KOA shrinkage control technology:

- ① The accuracy of the height direction is maintained, so the characteristics and accuracies of buried passive components are outstanding.

- ② When a cavity is formed, the stable one can be formed.

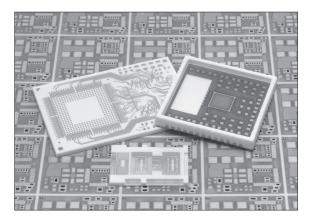

### ■ 用途 Applications

- ●使用微波、毫米波等的高频率的用途。

- ●在高温、高湿度等环境严酷的环境下也可以使用。

- 移动体通信模块。

- 裸形片多芯片模块。

- MEMS包装。

- ●转接基板

- UL1449(3rd Edition) (File No. E328032)

NVD05, NVD07: 82~470V, NVD10: 82~1100V, NVD14: 82~910V, NVD20: 200~910V

- Applications using high frequencies like micro-waves, milli-waves, etc.

- Applications used in harsh environment, especially in high temperatures, high humidities, etc.

- Small size mobile communication modules.

- Multi chip modules for bare chips.

- MEMS packages

- Interposer substrates.

#### ■ 品名构成 Type Designation

#### 实例 Example

预知关于此产品含有的环境负荷物质详情(除EU-RoHS以外),请与我们联系。

Contact us when you have control request for environmental hazardous material other than the substance specified by EU-RoHS.

## ■ LTCC是什么 What is LTCC

随着电子设备在高性能、轻薄短小方面的进展,在布线基板上也要求高性能。

作为对应基板高性能的技术之一,是LTCC(低温同步煅烧陶瓷)。

LTCC通过在氧化铝中加玻璃系材质,相比氧化铝在1500℃煅烧,可以在900℃以下的"低温"煅烧的陶瓷多层技术。

最大的特色是,通过低温煅烧,可以把银等低熔点材料在内部布线中使用。

With the high functioning and the advance in down-sizing of electronic equipment, wiring substrates are also required to be highly functioned. One of the technologies to respond to the high functioning of the substrates is LTCC(Low Temperature Co-fired Ceramics), which is the ceramic multilayer technology that enables the alumina to be fired at a "low temperature" of 900°C or lower by adding glass materials to the alumina while it is fired by a "high temperature" of about 1500°C.

It is the LTCC's important characteristics that low melting point materials like Ag, etc.can be used for the buried conductors for the low temperature firing.

#### ■ 基板材料特性 Characteristics of Substrate Material

| 项目<br>Parameter                 | 特性<br>Characteristics |  |

|---------------------------------|-----------------------|--|

|                                 | Characteristics       |  |

| 抗析强度(MPa)                       | 250                   |  |

| Bending strength                |                       |  |

| 热膨胀系数(×10 <sup>-6</sup> /K)     | 5.5                   |  |

| Thermal expansion coefficient   | 0.0                   |  |

| 热传导率(W/m • K)                   | 3                     |  |

| Thermal conductivity            |                       |  |

| 绝缘电阻 (Ω • cm)                   | >1013                 |  |

| Insulation resistance           |                       |  |

| 介电常数 at 1MHz                    | 7                     |  |

| Dielectric constant             |                       |  |

| 介质损耗 at 1MHz                    | < 0.003               |  |

| Dielectric loss                 |                       |  |

| 内部导体电阻 (μΩ•cm)                  | Ag 2.5                |  |

| Resistivity of buried conductor |                       |  |

| 密度 (g/cm³)                      |                       |  |

| Density                         | 2.8                   |  |

| 表面光洁度 Ra(μm)                    | < 0.4                 |  |

| Surface roughness Ra            | \U.4                  |  |

| 耐压 (kV/mm)                      | \ . I =               |  |

| Withstanding voltage            | >15                   |  |

| 层厚(μ m/Layer)                   | 00 100 105 07D        |  |

| Layer thickness                 | 80, 100, 125 STD.     |  |

#### ■ 设计规则 Design rule

| = KY NEXT Design rate |                                |                          |

|-----------------------|--------------------------------|--------------------------|

| 符号                    | ↓ 项目                           | 设计值                      |

| Symbol                | Parameter                      | Design value             |

| A                     | 线路宽度                           | 0.06mm Min.              |

|                       | Line width                     |                          |

| В                     | 线路间空间                          | 0.06mm Min.              |

|                       | Line to line spacing           |                          |

| С                     | 通路直径                           | 0.1mm, 0.15mm, 0.2mm     |

|                       | Via diameter                   |                          |

| D                     | 通路充填直径                         | Via diameter+0.05mm Min. |

|                       | Via pad diameter               |                          |

| E                     | 通路间隔                           | 0.2mm Min.               |

|                       | Via to via spacing             |                          |

| F                     | 通路-线路间隔                        | 0.15mm Min.              |

|                       | Via to line spacing            |                          |

| G                     | 模型层通路充填直径                      | 0.2mm Min.               |

|                       | Part edge to conductor spacing |                          |

| Н                     | 基板端模型间隔                        | 0.3mm Min.               |

|                       | Part edge to Via spacing       |                          |

| J1, J2                | 空腔宽度                           | 0.6mm Min.               |

|                       | Cavity width                   |                          |

| K1, K2                | 空腔深度                           | 0.1mm Min.               |

|                       | Cavity depth                   |                          |

| L                     | 空腔壁面厚度                         | 0.5mm Min.               |

|                       | Wall thickness of cavity       |                          |

| М                     | 空腔内隔板宽度                        | 0.5mm Min.               |

|                       | Shelf width in the cavity      | U.ƏHIIN MIN.             |